# TWO PHASE SYNCHRONOUS PWM CONTROLLER WITH INTEGRATED FET DRIVER, DIFFERENTIAL CURRENT SENSE & 5V BIAS REGULATOR

PRC8I 7HCB DATA SHEET Ph Free Product

## DESCRIPTION

# - FEATURES

The NX2423 is a two-phase PWM controller with integrated FET driver designed for low voltage high current application. The two phase synchronous buck converter offers ripple cancelation for both input and output. The NX2423 uses differential remote sensing using either current sense resistor or inductor DCR sensing to achieve accurate current matching between the two channels. Differential sensing eliminates the error caused by PCB board trace resistance that otherwise presents when using a single ended voltage sensing.

ing a single ended voltage sensing.

In addition the NX2423 offers high drive current capability especially for keeping the synchronous MOSFET off during SW node transition, can provide regulated 5V to IC biasing and drivers via 5V bias regulator, allows the slave channel on and off via EN2\_B pin while the main channel is working. Other features: PGOOD output, programmable switching frequency and hiccup current limiting circuitry.

- Differential inductor DCR sensing eliminates the problem with layout parasitic

- 5V bias regulator available

- Low Impedance On-board Drivers

- Hiccup current limit and IOUT indication

- Power Good for power sequencing

- EN2\_B pin allows the slave channel on and off while the master channel is working

- Programmable frequency

- Prebias start up

- OVP without negative spike at output

- Selectable between internal and external reference

- Internal Schottky diode from PVCC to BST

- Pb-free and RoHS compliant

# **APPLICATIONS**

- Graphic card High Current Vcore Supply

- High Current on board DC to DC converter applications

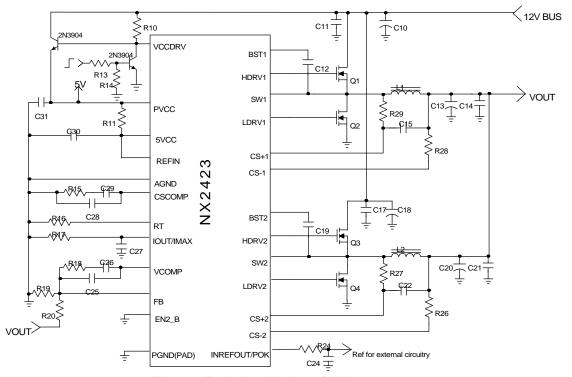

# TYPICAL APPLICATION

Figure 1 - Typical application of NX2423

## ORDERING INFORMATION

| Device     | Temperature | Package        | Frequency          | Pb-Free |

|------------|-------------|----------------|--------------------|---------|

| NX2423CMTR | 0 to 70°C   | MLPQ 4x4 - 24L | 50kHz to ) \$\$ Hz | Yes     |

# ABSOLUTE MAXIMUM RATINGS

| Vcc to PGND & BST to SW voltage                   | -0.3V to 6.5V  |  |  |  |

|---------------------------------------------------|----------------|--|--|--|

| BST to PGND Voltage                               | -0.3V to 35V   |  |  |  |

| SW to PGND                                        | -2V to 35V     |  |  |  |

| All other pins                                    | 0.3V to 6.5V   |  |  |  |

| Storage Temperature Range                         | -65°C To 150°C |  |  |  |

| Operating Junction Temperature Range40°C To 125°C |                |  |  |  |

| Lead temperature(Soldering 5s) 260°C              |                |  |  |  |

CAUTION: Stresses above those listed in "ABSOLUTE MAXIMUM RATINGS", may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

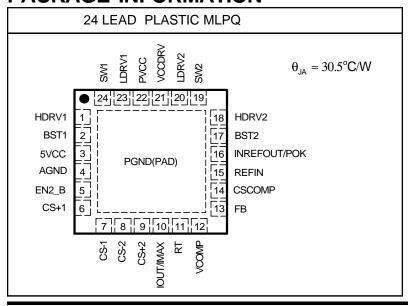

# **PACKAGE INFORMATION**

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over 5Vcc = 5V, PVcc = 5V,  $V_{BST}^{-}V_{SW}^{-}=5V$ ,  $EN2_B=GND$ , and  $T_A = 0$  to  $70^{\circ}C$ . Typical values refer to  $T_A = 25^{\circ}C$ . Low duty cycle pulse testing is used which keeps junction and case temperatures equal to the ambient temperature.

| PARAMETER                                                            | SYM                           | TEST CONDITION                                                             | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage(Vcc) 5V <sub>CC</sub> ,PV <sub>CC</sub> Voltage Range | V <sub>CC</sub>               |                                                                            | 4.5 | 5   | 5.5 | V     |

| 5V <sub>CC</sub> Supply Current (static)                             | I <sub>CC</sub> (Static)      | REFIN=GND, EN2_B=5V                                                        | -   | 6.7 |     | mA    |

| PV <sub>CC</sub> Supply Current (Dynamic)                            | ICC<br>(Dynamic)              | REFIN=5V, EN2_B=GND,<br>Freq=200Khz per phase<br>C <sub>LOAD</sub> =2200PF |     | 4.4 |     | mA    |

| V <sub>BST</sub> Voltage Range                                       | $V_{BST}$ to $V_{SW}$         |                                                                            | 4.5 | 5   | 5.5 | V     |

| V <sub>BST</sub> Supply Current ((Dynamic))                          | V <sub>BST</sub><br>(Dynamic) | REFIN=5V, EN2_B=GND,<br>Freq=200Khz per phase<br>C <sub>LOAD</sub> =2200PF |     | 4.5 |     | mA    |

| PARAMETER                   | SYM                                                             | TEST CONDITION                                | MIN     | TYP   | MAX  | UNITS           |

|-----------------------------|-----------------------------------------------------------------|-----------------------------------------------|---------|-------|------|-----------------|

| Under Voltage, Vcc & EN2_B  |                                                                 |                                               |         |       |      |                 |

| V <sub>CC</sub> -Threshold  | V <sub>CC</sub> _UVLO                                           | V <sub>CC</sub> Rising                        |         | 4.1   |      | V               |

| V <sub>CC</sub> -Hysteresis | V <sub>CC</sub> _Hyst                                           | 0                                             |         | 0.4   |      | V               |

| EN2_B Threshold             | , ,                                                             | V <sub>EN2 B</sub> Rising                     |         | 0.82  |      | V               |

| EN2_B Hysteresis            |                                                                 |                                               |         | 80    |      | mV              |

| Reference Voltage           |                                                                 |                                               |         |       |      |                 |

| Ref Voltage                 | $V_{REF}$                                                       | 4.5V<5Vcc<5.5V                                |         | 0.6   |      | V               |

| Ref Voltage line regulation |                                                                 |                                               |         | 0.2   |      | %               |

| Oscillator (Rt)             |                                                                 |                                               |         |       |      |                 |

| Frequency for each phase    | Fs                                                              | Rt=100kohm                                    |         | 400   |      | KHz             |

| Ramp-Amplitude Voltage      | $V_{RAMP}$                                                      |                                               |         | 1.02  |      | V               |

| Ramp Peak                   |                                                                 |                                               |         | 2.2   |      | V               |

| Ramp Valley                 |                                                                 |                                               |         | 1.18  |      | V               |

| Max Duty Cycle              |                                                                 | 200Khz/Phase                                  |         | 97    |      | %               |

| Min Duty Cycle              |                                                                 |                                               |         |       | 0    | %               |

| Transconductance            |                                                                 |                                               |         |       |      |                 |

| Amplifiers(CSCOMP)          |                                                                 |                                               |         |       |      |                 |

| Open Loop Gain              |                                                                 |                                               | 50      | 65    |      | dB              |

| Transconductance            |                                                                 |                                               |         | 1600  |      | umoh            |

| Voltage Mode Error          |                                                                 |                                               |         |       |      |                 |

| Open Loop Gain              |                                                                 |                                               | 50      |       |      | dB              |

| Input Offset Voltage        | Vio_v                                                           |                                               |         | 0     |      | mV              |

| Output Current Source       |                                                                 |                                               | 5       |       |      | mΑ              |

| Output Current Sink         |                                                                 |                                               | 5       |       |      | mΑ              |

| Output HI Voltage           |                                                                 |                                               | Vcc-1.5 |       |      | V               |

| Output LOW Voltage          |                                                                 |                                               |         |       | 0.5  | V               |

| SS (Internal )              |                                                                 |                                               |         |       |      |                 |

| Soft Start time             | Tss                                                             | 400Khz/Phase                                  |         | 2.5   |      | mS              |

| POK/INFEROUT                |                                                                 |                                               |         |       |      |                 |

| Threshold                   |                                                                 | V <sub>FB</sub> Rising                        |         | 73    |      | %V <sub>P</sub> |

| Hysteresis                  |                                                                 |                                               |         | 5     |      | %               |

| POK Voltage                 |                                                                 | I <sub>OUT</sub> =5mA(sourcing)               | 1.191   | 1.215 | 1.24 | V               |

| High Side Driver            |                                                                 |                                               |         |       |      |                 |

| (C <sub>L</sub> =4700pF)    |                                                                 |                                               |         |       |      |                 |

| Output Impedance , Sourcing | R <sub>source</sub> (Hdrv)                                      | I=200mA                                       |         | 1     |      | ohm             |

| Current                     |                                                                 |                                               |         |       |      |                 |

| Output Impedance , Sinking  | R <sub>sink</sub> (Hdrv)                                        | I=200mA                                       |         | 0.7   |      | ohm             |

| Current                     |                                                                 |                                               |         |       |      |                 |

| Rise Time                   | THdrv(Rise)                                                     | 10% to 90%                                    |         | 19    |      | ns              |

| Fall Time                   | THdrv(Fall)                                                     | 90% to 10%                                    |         | 18.5  |      | ns              |

| Deadband Time               | Tdead(L to<br>H)                                                | Ldrv going Low to Hdrv going<br>High, 10%-10% |         | 40    |      | ns              |

| Low Side Driver             |                                                                 |                                               |         |       |      |                 |

| (C <sub>L</sub> =10000pF)   |                                                                 |                                               |         |       |      |                 |

|                             |                                                                 | 1 000 A                                       |         | 1     |      | ohm             |

| Output Impedance, Sourcing  | R <sub>source</sub> (Ldrv)                                      | I=200mA                                       |         | ı     |      | 011111          |

| Current                     |                                                                 |                                               |         | ı     |      |                 |

|                             | $R_{\text{source}}(\text{Ldrv})$ $R_{\text{sink}}(\text{Ldrv})$ | I=200mA                                       |         | 0.5   |      | ohm             |

| PARAMETER                                    | SYM           | TEST CONDITION                                                   | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|---------------|------------------------------------------------------------------|------|------|------|-------|

| Rise Time                                    | TLdrv(Rise)   | 10% to 90%                                                       |      | 34   |      | ns    |

| Fall Time                                    | TLdrv(Fall)   | 90% to 10%                                                       |      | 18   |      | ns    |

| Deadband Time                                | Tdead(H to L) | SW going Low to Ldrv going<br>High, 10% to 10%                   |      | 10   |      | ns    |

| Propagation Delay                            | Tdealy(H)     | IN going High to Ldrv going Low                                  |      | 14   |      | ns    |

| Current Sense                                |               |                                                                  |      |      |      |       |

| Amplifier(CS+, CS-) Input Offset Voltage     |               |                                                                  | -2   |      | 2    | mV    |

| Voltage Gain                                 |               |                                                                  | 29.7 | 30   | 30.3 | V/V   |

| OVP Threshold OVP Threshold                  |               | percent of Vp                                                    |      | 130  |      | %     |

| FB UVLO Threshold FB UVLO Threshold          |               | percent of Vp                                                    |      | 70   |      | %     |

| REFIN VOLTAGE REFIN Voltage Range            |               |                                                                  | 0.4  |      | 2.5  | V     |

| Disable Voltage Threshold                    |               |                                                                  | 0.3  | 0.35 | 0.4  | V     |

| Threshold Enable Internal Reference          |               |                                                                  |      | 75   |      | %VCC  |

| 5V AUX REG                                   |               |                                                                  |      |      |      |       |

| Regout Output Voltage High                   |               | VIN=12V, PVCC=3V                                                 |      | 11   |      | V     |

| Regout Output Voltage Low                    |               | VIN=12V, PVCC=5.8V,<br>VCCDRV connected to 12V<br>by 1k resistor |      | 2    |      | V     |

| Internal Schottky Diode Forward voltage drop |               | forward current=10mA                                             |      | 600  |      | mV    |

11861 Western Avenue, Garden Grove, CA. 92841, 800-877-6458, 714-898-8121, Fax: 714-893-2570

| PIN DESCRIPTIONS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL           | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HDRV1            | High side gate driver for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| BST1             | Bootstrap supply for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 5VCC             | IC's supply voltage. This pin biases the internal logic circuits. A minimum 1uF ceramic capacitor is recommended to connect from this pin to ground plane.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| AGND             | Controller analog ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| EN2_B            | This pin is used to startup or shutdown the channel2 only while 5VCC and REFIN is ready. For two phase opeartion, EN2_B is preferred to be tied to GND. For one phase opeartion, EN2_B is preferred to be tied to 5VCC. During the operation, it is not recommended to change EN2_B voltage.                                                                                                                                                                                    |  |  |  |

| CS+1             | Positive input of the channel 1 differential current sense amplifiers. It is connected directly to the RC junction of the respective phase's output inductor.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CS-1             | Negative input of the channel 1 differential current sense amplifiers. It is connected directly to the negative side of the respective phase's output inductor.                                                                                                                                                                                                                                                                                                                 |  |  |  |

| CS-2             | Negative input of the channel 2 differential current sense amplifiers. It is connected directly to the negative side of the respective phase's output inductor.                                                                                                                                                                                                                                                                                                                 |  |  |  |

| CS+2             | Positive input of the channel 2 differential current sense amplifiers. It is connected directly to the RC junction of the respective phase's output inductor.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IOUT/IMAX        | This pin indicates average output current level and sets OCP threshold using a resistor from this pin to ground. A no more than 1nF ceramic capacitor is recommended to connect this pin to ground plane to filter the noise on this pin.                                                                                                                                                                                                                                       |  |  |  |

| RT               | This pin programs the internal oscillator frequency using a resistor from this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VCOMP            | This is the output pin of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| FB               | This pin is the error amplifier inverting input. It is connected to the output voltage via a voltage divider.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CSCOMP           | The output of the transconductance op amp for current balance circuit. An external RC is connected from this pin to GND to stabilize the current loop.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| REFIN            | External reference input. If pull-up to >4.5V, internal reference is used. If driven by an external voltage ranged from 0.4V to 2.5V, external reference is used with slew rate following SS rate. If REFIN is below 0.4V, device is disabled.                                                                                                                                                                                                                                  |  |  |  |

| INREFOUT/<br>POK | This pin has dual functions. When FB pin is below 75% of internal 0.6V reference, this pin is held low. When FB reaches above this threshold, this pin is tied to an internal 1.25V reference, allowing it to be used as a reference for any external op amp circuitry as well as an indicator of power OK. This pin can not be connected directly to an output capacitor. An RC network is needed which also provides a slow ramp up of the reference for the external op amp. |  |  |  |

6

| SYMBOL | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BST2   | Bootstrap supply for Channel 2.                                                                                                                                                                                                                                                                                                         |

| HDRV2  | High side gate driver for Channel 2.                                                                                                                                                                                                                                                                                                    |

| SW2    | Switch node for Channel2.                                                                                                                                                                                                                                                                                                               |

| LDRV2  | Low side gate driver for Channel 2.                                                                                                                                                                                                                                                                                                     |

| PVCC   | This pin provide the supply voltage for the lower MOSFET drivers. This pin provide the supply voltage for the lower MOSFET drivers. A high frequency ceramic 1uF must be placed close to this pin and tied to PGND to provide peak current needed for low side MOSFETs.                                                                 |

| LDRV1  | Low side gate driver for Channel 1.                                                                                                                                                                                                                                                                                                     |

| SW1    | Switch node for Channel 1.                                                                                                                                                                                                                                                                                                              |

| PGND   | This is the ground connection for the power stage of the controller.                                                                                                                                                                                                                                                                    |

| VCCDRV | The output of the 5V regulator controller that drives a low current low cost external BIPOLAR transistor or an external MOSFET to regulate the voltage at Vcc pin derived from BUS voltage. A resistor with value from 1k to 10k is used to connect VCCDRV and VBUS. Pulling down VCCDRV is used to disable chip in NX2423 application. |

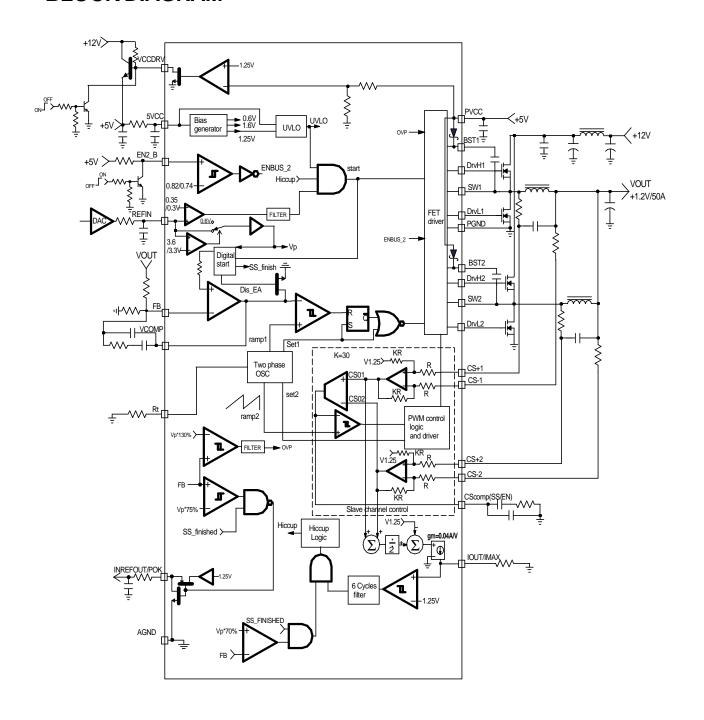

# **BLOCK DIAGRAM**

Figure 2 - Block diagram of NX2423

# **APPLICATION INFORMATION**

## **Symbol Used In Application Information:**

V<sub>IN</sub> - Input voltage V<sub>OUT</sub> - Output voltage

Iout - Output current

$\Delta V_{\text{RIPPLE}}$  - Output voltage ripple

Fs - Operation frequency for each channel

$\Delta$ IRIPPLE - Inductor current ripple

## **Design Example**

The following is typical application for NX2423.

$V_{IN} = 12V$

Vout=1.2V

**І**оит=50А

IOUT\_max=60A

$\Delta V_{RIPPLE} <= 12mV$

$\Delta V_{DROOP} <= 120 \text{mV} @ 30 \text{A step}$

Fs=400kHz

Phase number N=2

## **Output Inductor Selection**

The selection of inductor value is based on inductor ripple current, power rating, working frequency and efficiency. Larger inductor value normally means smaller ripple current. However if the inductance is chosen too large, it brings slow response and lower efficiency. Usually the ripple current ranges from 20% to 40% of the output current. This is a design freedom which can be decided by design engineer according to various application requirements. The inductor value can be calculated by using the following equations:

$$\begin{split} L_{\text{OUT}} &= \frac{V_{\text{IN}} - V_{\text{OUT}}}{\Delta I_{\text{RIPPLE}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \frac{1}{F_{\text{S}}} \\ \Delta I_{\text{RIPPLE}} &= k \times \frac{I_{\text{OUTPUT}}}{N} \end{split} ...(1)$$

where k is between 0.2 to 0.4.

Select k=0.2, then

$$L_{\text{OUT}} = \frac{12V - 1.2V}{0.2 \times \frac{50A}{2}} \times \frac{1.2V}{12V} \times \frac{1}{400 \text{kHz}}$$

$$L_{OUT} = 0.54uH$$

Choose inductor from Vishay IHLP\_5050FD-01 with L=0.68uH DCR=1.4m $\Omega$ .

Current Ripple is recalculated as

$$\Delta I_{\text{RIPPLE}} = \frac{V_{\text{IN}} - V_{\text{OUT}}}{L_{\text{OUT}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \frac{1}{F_{\text{S}}}$$

$$= \frac{12V - 1.2V}{0.68uH} \times \frac{1.2V}{12V} \times \frac{1}{400kHz} = 3.97A \quad ...(2)$$

## **Output Capacitor Selection**

Output capacitor value is basically decided by the output voltage ripple, capacitor RMS current rating and load transient.

#### **Based on Voltage Ripple**

For electrolytic, POSCAP bulk capacitor, the ESR (equivalent series resistance) and inductor current typically determines the output voltage ripple.

$$ESR_{desire} = \frac{\Delta V_{RIPPLE}}{\Delta I_{RIPPLE}} = \frac{12mV}{3.97A} = 3.022m\Omega \qquad ...(3)$$

If low ESR is required, for most applications, multiple capacitors in parallel are better than a big capacitor. For example, for 12mV output ripple, SANYO OSCON capacitors 2R5SEPC1000MX(1000uF 7m $\Omega$ ) are chosen.

$$N = \frac{E S R_E \times \Delta I_{RIPPLE}}{\Delta V_{RIPPLE}} ...(4)$$

Number of Capacitor is calculated as

$$N = \frac{7m\Omega \times 3.97A}{12mV}$$

N = 2.3

For ceramic capacitor, the current ripple is determined by the number of capacitor instead of ESR

$$C_{\text{OUT}} = \frac{\Delta I_{\text{RIPPLE}}}{8 \times F_{\text{S}} \times \Delta V_{\text{RIPPLE}}} \qquad ...(5)$$

Typically, the calculated capacitance is so small that the output voltage droop during the transient can not meet the spec although ripple is small.

#### **Based On Transient Requirement**

Typically, the output voltage droop during transient is specified as:

$$\Delta V_{DROOP} < \Delta V_{TRAN}$$

@ step load  $\Delta I_{STEP}$

During the transient, the voltage droop during the transient is composed of two sections. One Section is dependent on the ESR of capacitor, the other section is a function of the inductor, output capacitance as well as input, output voltage. For example, overshoot caused by  $\Delta I_{\text{STEP}}$  transient load which is from high load to low load, can be estimated as the following equation,if assuming the bandwidth of system is high enough.

$$\Delta V_{\text{overshoot}} = ESR \times \Delta I_{\text{step}} + \frac{V_{\text{OUT}}}{2 \times L \times C_{\text{OUT}}} \times \tau^2 \qquad ...(6)$$

where t is the a function of capacitor, etc.

$$\tau = \begin{cases} 0 & \text{if } L_{\text{EFF}} \leq L_{\text{crit}} \\ \frac{L_{\text{EFF}} \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - \text{ESR} \times C_{\text{OUT}} & \text{if } L_{\text{EFF}} \geq L_{\text{crit}} \end{cases} \dots (7)$$

where

$$\begin{split} L_{\text{EFF}} &= \frac{L_{\text{OUT}}}{N} = \frac{0.68 \text{uH}}{2} = 0.34 \text{uH} \\ L_{\text{crit}} &= \frac{ESR \times C_{\text{OUT}} \times V_{\text{OUT}}}{\Delta I_{\text{step}}} = \frac{ESR_{\text{E}} \times C_{\text{E}} \times V_{\text{OUT}}}{\Delta I_{\text{step}}} \quad ... \text{(8)} \end{split}$$

where  ${\rm ESR_E}$  and  ${\rm C_E}$  represents ESR and capacitance of each capacitor if multiple capacitors are used in parallel.

The above equation shows that if the selected output inductor is smaller than the critical inductance, the voltage droop or overshoot is only dependent on the ESR of output capacitor. For low frequency capacitor such as electrolytic capacitor, the product of ESR and capacitance is high and  $L \! \leq \! L_{\rm crit}$  is true. In that case, the transient spec is dependent on the ESR of capacitor.

In most cases, the output capacitors are multiple capacitors in parallel. The number of capacitors can be calculated by the following

$$N = \frac{ESR_E \times \Delta I_{step}}{\Delta V_{tran}} + \frac{V_{OUT}}{2 \times L \times C_E \times \Delta V_{tran}} \times \tau^2 \qquad ...(9)$$

where

$$\tau = \begin{cases} 0 & \text{if } L_{\text{EFF}} \leq L_{\text{crit}} \\ \frac{L_{\text{EFF}} \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - ESR_{\text{E}} \times C_{\text{E}} & \text{if } L_{\text{EFF}} \geq L_{\text{crit}} & \dots \text{(10)} \end{cases}$$

For example, assume voltage droop during transient is 120mV for 30A load step.

If the OS-CON capacitors (1000uF,  $7m\Omega$  ) is used, the critical inductance is given as

$$\begin{split} L_{crit} &= \frac{ESR_{E} \times C_{E} \times V_{OUT}}{\Delta I_{step}} = \\ &\frac{7m\Omega \times 1000 \mu F \times 1.2 V}{30A} = 0.28 \mu H \end{split}$$

The effective inductor value is 0.34uH which is bigger than critical inductance. In that case, the output voltage transient not only dependent on the ESR, but also capacitance.

number of capacitors is

$$\begin{split} \tau &= \frac{L_{\text{EFF}} \times \Delta I_{\text{step}}}{V_{\text{OUT}}} - ESR_{\text{E}} \times C_{\text{E}} \\ &= \frac{0.34 \mu H \times 30 A}{1.2 V} - 7 m \Omega \times 1000 \mu F = 1.5 us \end{split}$$

$$\begin{split} N = & \frac{ESR_E \times \Delta I_{step}}{\Delta V_{tran}} + \frac{V_{OUT}}{2 \times L_{EFF} \times C_E \times \Delta V_{tran}} \times \tau^2 \\ = & \frac{7m\Omega \times 30A}{120mV} + \\ & \frac{1.2V}{2 \times 0.34 \mu H \times 1000 \mu F \times 120mV} \times (1.5us)^2 \\ = & 1.78 \end{split}$$

The number of capacitors has to satisfied both ripple and transient requirement. Overall, we can choose N=2.

It should be considered that the proposed equation is based on ideal case, in reality, the droop or overshoot is typically more than the calculation. The equation gives a good start. For more margin, more capacitors have to be chosen after the test. Typically, for high frequency capacitor such as high quality POSCAP especially ceramic capacitor, 20% to 100% (for ceramic) more capacitors have to be chosen since the ESR of capacitors is so low that the PCB parasitic can affect the results tremendously. More capacitors have to be selected to compensate these parasitic parameters.

## **Control Loop Compensator Design**

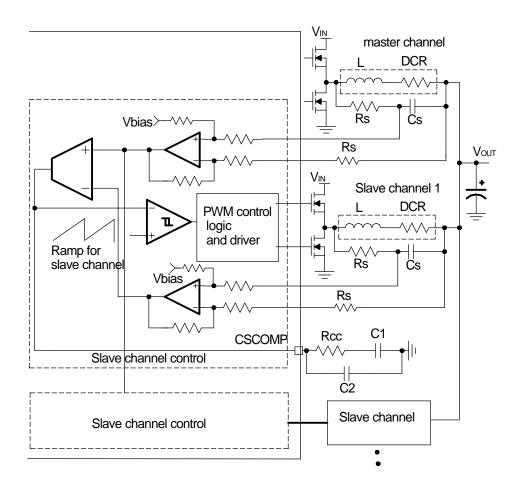

NX2423 can control and drive two channel synchronous bucks with 180° phase shift between each other. One of two channels is called master, the other is called slave. They are connected together by sharing the same output capacitors. Voltage loop is designed to regulate output voltage. In order to achieve the current balance in these two synchronous buck converters, current loop compensation network is employed to to make sure the currents in slave is following the master.

## **Voltage Loop Compensator Design**

Due to the double pole generated by LC filter of the power stage, the power system has 180° phase shift, and therefore, is unstable by itself. In order to achieve accurate output voltage and fast transient response, compensator is employed to provide highest possible bandwidth and enough phase margin. Ideally, the Bode plot of the closed loop system has crossover frequency between 1/10 and 1/5 of the switching frequency, phase margin greater than 50° and the gain crossing 0dB with -20dB/decade. Power stage output capacitors usually decide the compensator type. If electrolytic capacitors are chosen as output capacitors, type II compensator can be used to compensate the system, because the zero caused by output capacitor ESR is lower than crossover frequency. Otherwise type III compensator should be chosen.

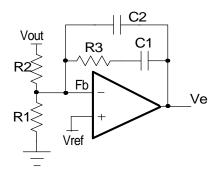

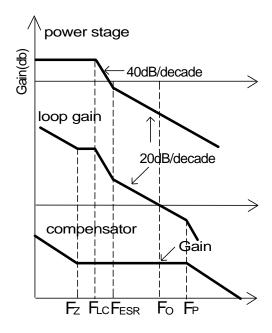

#### A. Type II compensator design

If the electrolytic capacitors are chosen as power stage output capacitors, usually the Type II compensator can be used to compensate the system.

Type II compensator can be realized by simple RC circuit without feedback as shown in figure 3. R3 and C1 introduce a zero to cancel the double pole effect. C2 introduces a pole to suppress the switching noise. The following equations show the compensator pole zero location and constant gain.

$$Gain = \frac{R_3}{R_2} \qquad ... (11)$$

$$F_z = \frac{1}{2 \times \pi \times R_3 \times C_1} \qquad \dots (12)$$

$$F_p \approx \frac{1}{2 \times \pi \times R_3 \times C_2}$$

... (13)

Figure 3 - Type II compensator

Figure 4 - Bode plot of Type II compensator

For this type of compensator,  $F_{\rm o}$  has to satisfy  $F_{\rm LC} < F_{\rm ESR} << F_{\rm o}$  and  $F_{\rm o} <=1/10 \sim 1/5 F_{\rm s}$ .

Here a type II compensator is designed for the case which has six electrolytic capacitors (1800 uF,  $13m\Omega$ ) and

two 1.5uH inductors.

1.Calculate the location of LC double pole  $\rm F_{LC}$  and ESR zero  $\rm F_{ESR}.$

$$\begin{split} F_{LC} = & \frac{1}{2 \times \pi \times \sqrt{L_{EFF} \times C_{OUT}}} \\ = & \frac{1}{2 \times \pi \times \sqrt{0.75 uH \times 10800 uF}} \\ = & 1.768 kHz \end{split}$$

$$F_{\text{ESR}} = \frac{1}{2 \times \pi \times \text{ESR} \times \text{C}_{\text{OUT}}}$$

$$= \frac{1}{2 \times \pi \times 13 \text{m}\Omega \times 1800 \text{uF}}$$

$$= 6.801 \text{kHz}$$

2.Set  $R_2$  equal to  $10k\Omega$  and calculate  $R_1$ .

$$R_1 = \frac{R_2 \times V_{REF}}{V_{OUT} \cdot V_{REF}} = \frac{10k\Omega \times 0.6V}{1.2V \cdot 0.6V} = 10k\Omega$$

- 3. Set crossover frequency Fo=15kHz.

- 4. Calculate  $R_3$  value by the following equation.

$$R_{3} = \frac{V_{OSC}}{V_{in}} \times \frac{2 \times \pi \times F_{O} \times L_{EFF}}{ESR} \times R_{2}$$

$$= \frac{1V}{12V} \times \frac{2 \times \pi \times 15 \text{kHz} \times 0.75 \text{uH}}{2.16 \text{m}\Omega} \times 10 \text{k}\Omega$$

$$= 27.3 \text{k}\Omega$$

Choose  $R_3 = 27.4k\Omega$ .

5. Calculate  $C_1$  by setting compensator zero  $F_2$  at 75% of the LC double pole.

$$C_1 = \frac{1}{2 \times \pi \times R_3 \times F_z}$$

$$= \frac{1}{2 \times \pi \times 27.4 \text{k}\Omega \times 0.75 \times 1.768 \text{kHz}}$$

=4.4nF

Choose C₁=4.7nF.

6. Calculate  $\boldsymbol{C}_2$  by setting compensator pole  $\boldsymbol{F}_p$  at half the swithing frequency.

$$C_{2} = \frac{1}{\pi \times R_{3} \times F_{s}}$$

$$= \frac{1}{\pi \times 27.4 k\Omega \times 400 kHz}$$

$$= 30 pF$$

Choose C<sub>2</sub>=33pF.

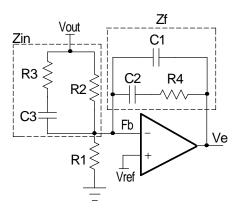

#### B. Type III compensator design

For low ESR output capacitors, typically such as Sanyo OSCON and POSCAP, the frequency of ESR zero caused by output capacitors is higher than the cross-over frequency. In this case, it is necessary to compensate the system with type III compensator.

In design example, six electrolytic capacitors are used as output capacitors. The system is compensated with type III compensator. The following figures and equations show how to realize the this type III compensator with electrolytic capacitors.

$$F_{z_1} = \frac{1}{2 \times \pi \times R_A \times C_2} \qquad \dots (14)$$

$$F_{z2} = \frac{1}{2 \times \pi \times (R_2 + R_3) \times C_3}$$

...(15)

$$F_{p_1} = \frac{1}{2 \times \pi \times R_3 \times C_3}$$

...(16)

$$F_{P2} = \frac{1}{2 \times \pi \times R_4 \times \frac{C_1 \times C_2}{C_4 + C_2}} \qquad \dots (17)$$

where  $\mathsf{F}_{\mathsf{Z}1}, \mathsf{F}_{\mathsf{Z}2}, \mathsf{F}_{\mathsf{P}1}$  and  $\mathsf{F}_{\mathsf{P}2}$  are poles and zeros in the compensator.

Figure 5 - Type III compensator

Figure 6 - Bode plot of Type III compensator

The transfer function of type III compensator is given by:

$$\frac{V_{e}}{V_{\text{OUT}}} = \frac{1}{sR_{2} \times (C_{2} + C_{1})} \times \frac{(1 + sR_{4} \times C_{2}) \times \left[1 + s(R_{2} + R_{3}) \times C_{3}\right]}{(1 + sR_{4} \times \frac{C_{2} \times C_{1}}{C_{2} + C_{1}}) \times \left(1 + sR_{3} \times C_{3}\right)}$$

Use the same power stage requirement as demo board. The crossover frequency has to be selected as  $F_{LC} < F_{ESR} < F_o$ , and usually  $F_o <= 1/10 \sim 1/5F_s$ .

1.Calculate the location of LC double pole  $\rm F_{LC}$  and ESR zero  $\rm F_{ESR}.$

$$\begin{split} F_{LC} &= \frac{1}{2 \times \pi \times \sqrt{L_{EFF} \times C_{OUT}}} \\ &= \frac{1}{2 \times \pi \times \sqrt{0.34 uH \times 2000 uF}} \\ &= 6.1 kHz \end{split}$$

$$F_{ESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

$$= \frac{1}{2 \times \pi \times 3.5 \text{m}\Omega \times 2000 \text{uF}}$$

$$= 22.7 \text{kHz}$$

2.Set R<sub>2</sub> equal to 10kΩ.

$$R_1 = \frac{R_2 \times V_{REF}}{V_{OUT} - V_{REF}} = \frac{10k\Omega \times 0.6V}{1.2V - 0.6V} = 10k\Omega$$

Choose  $R_1=10k\Omega$ .

3. Calculate  $C_3$  by setting  $F_{Z2} = F_{LC}$  and  $F_{p1} = F_{ESR}$ .

$$C_{3} = \frac{1}{2 \times \pi \times R_{2}} \times (\frac{1}{F_{z2}} - \frac{1}{F_{p1}})$$

$$= \frac{1}{2 \times \pi \times 10 \text{k}\Omega} \times (\frac{1}{6.1 \text{kHz}} - \frac{1}{22.7 \text{kHz}})$$

$$= 1.9 \text{nF}$$

Choose C<sub>3</sub>=1.8nF.

5. Calculate R<sub>3</sub> by equation (13).

$$R_{3} = \frac{1}{2 \times \pi \times F_{P1} \times C_{3}}$$

$$= \frac{1}{2 \times \pi \times 22.7 \text{kHz} \times 1.8 \text{nF}}$$

$$= 3.89 \text{k}\Omega$$

Choose  $R_3 = 3.92 k\Omega$ .

6. Calculate R<sub>4</sub> by choosing F<sub>0</sub>=40kHz.

$$\begin{split} R_4 &= \frac{V_{OSC}}{V_{in}} \times \frac{2 \times \pi \times F_O \times L_{EFF}}{ESR} \times \frac{R_2 \times R_3}{R_2 + R_3} \\ &= \frac{1V}{12V} \times \frac{2 \times \pi \times 40 \text{kHz} \times 0.34 \text{uH}}{3.5 \text{m}\Omega} \times \frac{10 \text{k}\Omega \times 3.92 \text{k}\Omega}{10 \text{k}\Omega + 3.92 \text{k}\Omega} \\ &= 5.73 \text{k}\Omega \end{split}$$

Choose  $R_{\lambda}$ =5.62k $\Omega$ .

7. Calculate  $C_2$  with zero  $F_{z1}$  at 75% of the LC double pole by equation (11).

$$\begin{aligned} C_2 &= \frac{1}{2 \times \pi \times F_{z_1} \times R_4} \\ &= \frac{1}{2 \times \pi \times 0.75 \times 6.1 \text{kHz} \times 5.62 \text{k}\Omega} \\ &= 6.2 \text{nF} \end{aligned}$$

Choose C<sub>2</sub>=6.8nF.

8. Calculate  $\rm C_1$  by equation (14) with pole  $\rm F_{\rm p2}$  at half the switching frequency.

$$C_{1} = \frac{1}{2 \times \pi \times R_{4} \times F_{P2}}$$

$$= \frac{1}{2 \times \pi \times 5.62 \text{k}\Omega \times 200 \text{kHz}}$$

$$= 141 \text{pF}$$

Choose C₁=150pF.

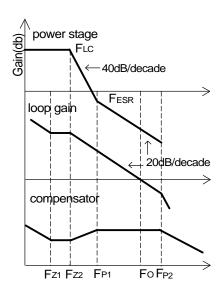

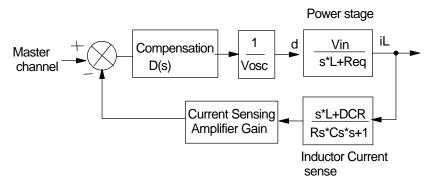

# **Current Loop Compensator Design**

Figure 7 - Current loop control diagram

Figure 8 - Function diagram of current loop

#### **Inductor Current Sensing**

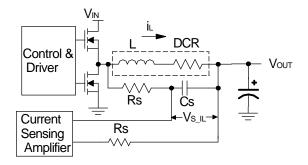

Figure 9 - Inductor current sensing using RC network.

The inductor current can be sensed through a RC network as shown above. The advantage of the RC network is the lossless comparing with a resistor in series with output inductor.

The selection of the resistor sensing network is chosen by the following equation:

$$R_S \times C_S = \frac{L}{DCR}$$

...(18)

If the above equation is satisfied, the voltage across the sensing capacitor Cs will be equal to the inductor current times DCR of inductor for all frequency domain.

$$V_{S IL} = DCR \times i_{L}$$

If the sensing capacitor is chosen

$$C_s = 1\mu F$$

C<sub>s</sub> must be X7R or COG ceramic capacitor. The sensing resistor is calculated as

$$R_{s} = \frac{L}{DCR \times C_{s}}$$

For example, for 0.68uH inductor with 1.4m $\Omega$  DCR, we have

$$R_s = \frac{0.68\mu H}{1.4m\Omega \times 1\mu F} = 486\Omega$$

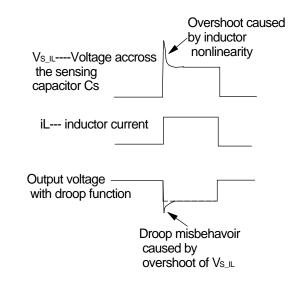

In most of cases, the selection of sensing resistor based on the above equation will be sufficient. However, for some inductor such as toroid coiled inductor with micrometal, even the product of sensing resistor and capacitor is perfectly match with L/DCR, the voltage across the capacitor still has overshoot due to the nonlinearity of inductor. This will affect the droop accu-

racy during the transient if droop function is required. The illustration is shown in the following figure.

Figure 10 - Droop accuracy affected by the nonlinearity of inductor.

In this case, the sensing resistor has to be chosen

$$R_s \ge \frac{L}{DCR \times C_s}$$

to compensate the overshoot. This selection only affects the small signal mode of current loop. For DC accuracy, there is no effect since the DC voltage across the sensing capacitor will equal to the DCR times inductor current at DC load no matter what Rs is. In this example, Rs=620 $\Omega$ .

$\rm R_s$  value is preferred to be less than  $400\Omega$  in NX2423's application, therefore we need to reiterate the calculation, choose  $\rm C_s$  2.2uF instead.  $\rm R_s$  value is finally chosen as  $301\Omega$  .

Powe dissipation of Rs resistor is calculated as followed:

$$P_{D}(R_{S}) = \frac{(V_{IN} - V_{OUT})^{2}}{R_{S}} \times D + \frac{V_{OUT}^{2}}{R_{S}} \times (1 - D)$$

$$= \frac{(12V - 1.2V)^{2}}{301\Omega} \times 0.1 + \frac{(1.2V)^{2}}{301\Omega} \times (1 - 0.1)$$

$$= 0.04W$$

The power rating of Rs should be over 0.04W.

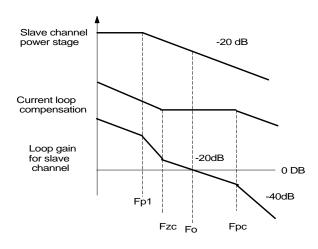

#### **Current Loop Compensation**

Figure 11 - Bode plot of current loop

The diagram and bode plot for current loop of NX2423 is shown in above figure. The current signal through inductor sensing is amplified by current sensing differential amplifier. The amplified slave current signal is compared with the amplified inductor current from master channel (channel 1 for NX2423) through a transconductance amplifier, the difference between channel current will change the output of transconductance amplifier, which will compare with a internal ramp signal and changes the duty cycle of slave channel buck converter. If the inductor are perfectly matched and the PWM controller has no offset, the DC current in slave channel will equal to the DC current of master channel (channel 1) due to the gain of current loop.

From the bode plot, the power stage has one pole located at

$$\mathsf{F}_{\mathsf{Pl}} = \frac{\mathsf{R}_{\mathsf{eq}}}{2 \times \pi \times \mathsf{L}}$$

where  $R_{eq}$  is the equivalent resistor and it is given by

$$R_{\text{eq}} \approx \text{DCR} + R_{\text{dson\_con}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} + R_{\text{dson\_syn}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

$R_{dson\_con}$  is the Rdson of control FET and  $R_{dson\_syn}$  is the Rdson of synchronous FET. For this example,

$$R_{eq} = 7.4 m\Omega$$

The pole is located as

$$\textit{F}_{_{\textrm{Pl}}} = \frac{\textit{R}_{_{\textrm{eq}}}}{2 \times \pi \times \textit{L}} = \frac{7.4 \text{m}\Omega}{2 \times \pi \times 0.68 \mu \textrm{H}} = 1.7 \textrm{kHz}$$

The current compensation transfer function is given as

$$D(s) = \frac{g_m}{s \times (C_1 + C_2)} \times \frac{1 + s \times R_{cc} \times C_1}{1 + s \times \frac{R_{cc} \times C_1 \times C_2}{C_1 + C_2}}$$

It has one zero and one pole. The ideal is to choose resistor Rcc to achieve desired loop gain such as 50kHz. Rcc can be calculated as

$$R_{cc} = \frac{2 \times \pi \times F_{o} \times L \times V_{osc}}{g_{m} \times V_{IN} \times K_{c} \times DCR} \qquad ...(19)$$

where

$$K_{\rm C} \approx \frac{60 \cdot k\Omega}{2k\Omega + R_{\rm S}} = 22.9$$

$60 k\Omega$  and  $2 k\Omega$  is the internal resistance for the current sensing amplifier.

For fast response, we can set the current loop cross-over frequency one and half times of voltage loop cross-over frequency. Since the voltage loop cross-over frequency is typically selected as 1/10 of switching frequency, we choose  $F_0=50$ kHz.

$$R_{cc} = \frac{2 \times \pi \times 50 \text{kHz} \times 0.68 \mu \text{H} \times 1\text{V}}{1.6 \text{mA} / \text{V} \times 12 \text{V} \times 22.9 \times 1.4 \text{m}\Omega} = 442 \Omega$$

Select

$$R_{cc} = 430\Omega$$

.

The selection of capacitor  $C_1$  is such that the zero of compensation will cancel the pole of power stage, therefore.

$$C_{_{1}} = \frac{L}{R_{_{eq}} \times R_{_{cc}}} = \frac{0.68 \mu H}{7.4 m\Omega \times 430 \Omega} = 214 nF$$

Typically, the capacitor  $\mathrm{C_1}$  is so big that the current loop may start slowly during the start up. Therefore, smaller capacitor can be selected. However, the selected capacitor can not reduce too much to cause phase droop.

Select C<sub>4</sub>=220nF.

The capacitor  $\mathbf{C}_2$  is an option and it is used to filter out the switching noise.  $\mathbf{C}_2$  can be calculated as

$$\begin{aligned} \mathbf{C}_2 &= \frac{1}{\pi \times \mathbf{R}_{cc} \times \mathbf{F_S}} = \frac{1}{\pi \times 430\Omega \times 400 \text{kHz}} = 1.85 \text{nF} \\ \text{Select C}_2 &= 2.2 \text{nF}. \end{aligned}$$

## **Frequency Selection**

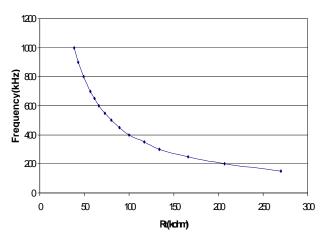

The frequency can be set by external Rt resistor. The relationship between frequency per phase and RT pin around 400kHz is shown as follows.

$$R_{T} \approx \frac{40000000}{F_{s}}$$

...(20)

#### Frequency(kHz) vsRt(kdm)

Figure 12 - Frequency vs Rt chart

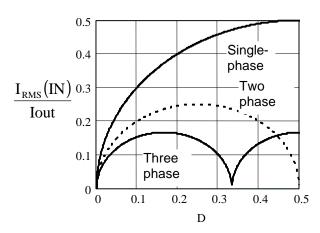

#### Input Filter Selection

The selection criteria of input capacitor are voltage rating and the RMS current rating. For conservative consideration, the capacitor voltage rating should be 1.5 times higher than the maximum input voltage. The RMS current rating of the input capacitor for multi-phase converter can be estimated from the above Figure 13.

First, determine the duty cycle of the converter ( $V_{o}/V_{IN}$ ). The ratio of input RMS current over output current can be obtained. Then the total input RMS current can be calculated. From this figure, it is obvious that a multiphase converter can have a much smaller input RMS current, which results in a lower amount of input capacitors that are required.

For example, Vin=12V, Vout=1.2V. The duty cycle is D=Vout/Vin=1.2/12=10%. From the figure, for two phase, the normlized RMS current is

0.2\*lout=0.2\*50A=10A.

A combination of ceramic and electrolytic(SANYO WG or WF series) or OSCON type capacitors can achieve both ripple current capability together with having enough capacitance such that input voltage will not sag too much. In this application, one OSCON SVPC180M(180uF, 16V, 2.8A) and three 10uF X5R ceramic capacitors are selected.

A 1uH input inductor is recommended to slow down the input current transient. Suppose power stage efficiency is 0.8, then input current can estimated by

$$I_{INPUT} = \frac{I_{OUT} \times V_{OUT}}{\eta \times V_{IN}} = \frac{60 \text{ A} \times 1.2 \text{ V}}{0.8 \times 12 \text{ V}} = 7.5 \text{ A}$$

In this application, Coilcraft DO3316P\_102HC with RMS rating 10A is chosen.

Figure 13 - Normalized input RMS current vs. duty cycle

#### **Over Current/Short Circuit Protection**

The converter will go into hiccup mode if the output current reaches a programmed limit  $I_{\text{OCP}}$  determined by the resistor value  $R_{\text{ocp}}$  at pin IOUT/IMAX.

$$R_{\text{OCP}} = \frac{1.25\text{V}}{0.04\text{mA/V}} \times \frac{2\text{k}\Omega + R_{\text{S}}}{60\text{k}\Omega} \times \frac{2}{\text{DCR}} \times \frac{1}{I_{\text{OCP}}} \qquad ...(21)$$

Where  $\rm I_{ocp}$  is the desired over current protection level,  $\rm R_s$  is the current sensing matching resistor when using DCR sensing method.

## **Over Voltage Protection**

Over voltage protection is achieved by sensing the output voltage through resistor divider. The sensed voltage on FB pin is compared with 130%\*V $_{\rm REF}$  to generate the OVP signal.

#### **Power MOSFETs Selection**

The NX2423 requires two N-Channel power MOSFETs for each channels. The selection of MOSFETs is based on maximum drain source voltage, gate source voltage, maximum current rating, MOSFET on resistance and power dissipation. The main consideration is the power loss contribution of MOSFETs to the overall converter efficiency. In this design example, eight NTD60N02 are used. They have the following parameters:  $V_{DS}$ =25V,  $I_{D}$ =62A,  $R_{DSON}$ =12m $\Omega$ ,  $Q_{GATE}$ =9nC.

There are three factors causing the MOSFET power loss:conduction loss, switching loss and gate driver loss.

Gate driver loss is the loss generated by discharging the gate capacitor and is dissipated in driver circuits. It is proportional to frequency and is defined as:

$$P_{gate} = (Q_{HGATE} \times V_{HGS} + Q_{LGATE} \times V_{LGS}) \times F_{S}$$

(22)

where  $Q_{\text{HGATE}}$  is the high side MOSFETs gate charge,  $Q_{\text{LGATE}}$  is the low side MOSFETs gate charge,  $V_{\text{HGS}}$  is the high side gate source voltage, and  $V_{\text{LGS}}$  is the low side gate source voltage. This power dissipation should not exceed maximum power dissipation of the driver device.

Conduction loss is simply defined as:

$$\begin{split} &P_{HCON} \! = \! I_{OUT}^{2} \times D \times R_{DS(ON)} \times K \\ &P_{LCON} \! = \! I_{OUT}^{2} \times (1 \! - \! D) \times R_{DS(ON)} \times K \\ &P_{TOTAL} \! = \! P_{HCON} + P_{LCON} \end{split} \qquad ...(23)$$

Where the R<sub>DS(ON)</sub> will increases as MOSFET junction temperature increases, K is R<sub>DS(ON)</sub> temperature dependency and should be selected for the worst case. Conduction loss should not exceed package rating or overall system thermal budget.

Switching loss is mainly caused by crossover conduction at the switching transition. The total switching loss can be approximated.

$$P_{SW} = \frac{1}{2} \times V_{IN} \times I_{OUT} \times T_{SW} \times F_{S} \qquad ...(24)$$

$\rm T_{SW}$  is the sum of  $\rm T_R$  and  $\rm T_F$  which can be found in mosfet datasheet, lout is output current, and Fs is switching frequency. Swithing loss  $\rm P_{SW}$  is frequency dependent.

## Soft Start and Enable Signal Operation

The NX2423's master channel will start operation after 5VCC and REFIN have reached their threshold voltages. Pulling down VCCDRV will cause 5VCC drop below to its threshold, then shuts down NX2423.

The slave channel will start operation only when EN2\_B is less than 0.8V, 5VCC and REFIN have reached their respective thresholds. For two phase opeartion, EN2\_B is preferred to be tied to GND. For one phase opeartion, EN2\_B is preferred to be tied to 5VCC. During the operation, it is not recommended to change EN2\_B voltage.

Once the converter starts, there is a soft start sequence of 1024 steps between 0 and  $V_{\rm REF}$ . The ramp rate is determined by the switching frequency.

$$\frac{dV_O}{dt} = \frac{V_O}{1024 \times T_S} \qquad ...(25)$$

# **Layout Considerations**

The layout is very important when designing high frequency switching converters. Layout will affect noise pickup and can cause a good design to perform with less than expected results.

There are two sets of components considered in the layout which are power components and small signal components. Power components usually consist of input capacitors, high-side MOSFET, low-side MOSFET, inductor and output capacitors. A noisy environment is generated by the power components due to the switching power. Small signal components are connected to sensitive pins or nodes. A multilayer layout which includes power plane, ground plane and signal plane is recommended.

Layout guidelines:

1. First put all the power components in the top layer connected by wide, copper filled areas. The input capacitor, inductor, output capacitor and the MOSFETs should be close to each other as possible. This helps to reduce the EMI radiated by the power loop due to the

high switching currents through them.

- 2. Low ESR capacitor which can handle input RMS ripple current and a high frequency decoupling ceramic cap which usually is 1uF need to be practically touching the drain pin of the upper MOSFET, a plane connection is a must.

- The output capacitors should be placed as close as to the load as possible and plane connection is required.

- 4. Drain of the low-side MOSFET and source of the high-side MOSFET need to be connected thru a plane ans as close as possible. A snubber nedds to be placed as close to this junction as possible.

- 5. Source of the lower MOSFET needs to be connected to the GND plane with multiple vias. One is not enough. This is very important. The same applies to the output capacitors and input capacitors.

- 6. Hdrv and Ldrv pins should be as close to MOSFET gate as possible. The gate traces should be wide and short. A place for gate drv resistors is needed to fine tune noise if needed.

- 7. Vcc capacitor, BST capacitor or any other bypassing capacitor needs to be placed first around the IC and as close as possible. The capacitor on comp to GND or comp back to FB needs to be place as close to the pin as well as resistor divider.

- 8. The output sense line which is sensing output back to the resistor divider should not go through high frequency signals.

- 9. All GNDs need to go directly thru via to GND plane.

- 10. The feedback part of the system should be kept away from the inductor and other noise sources, and be placed close to the IC.

- 11. In multilayer PCB, separate power ground and analog ground. These two grounds must be connected together on the PC board layout at a single point. The goal is to localize the high current path to a separate loop that does not interfere with the more sensitive analog control function.

- 12. Inductor current sense line should be connected directly to the inductor solder pad.

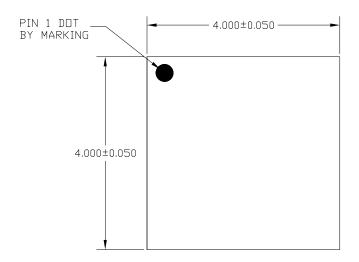

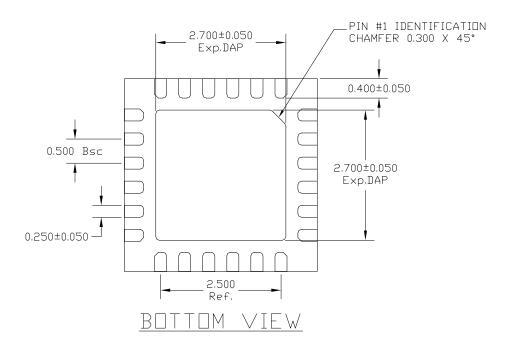

# MLPQ 24 PIN 4 x 4 PACKAGE OUTLINE DIMENSIONS

# TOP VIEW

SIDE VIEW

NOTE: ALL DIMENSIONS ARE DISPLAYED IN MILLIMETERS.

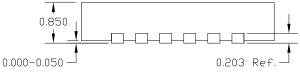

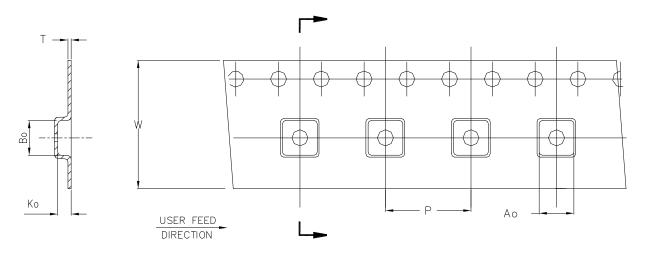

# MLPQ 24 PIN 4 x 4 TAPE AND REEL INFORMATION

| Dimension    | MLPQ 04X04   |

|--------------|--------------|

| Ао           | 4.35 +/- 0.1 |

| Во           | 4.35 +/- 0.1 |

| Ко           | 1.1 +/- 0.1  |

| Р            | 8 +/- 0.1    |

| W            | 12 +/- 0.3   |

| Т            | 0.3 +/- 0.05 |

| R7/Quantity  | 1000         |

| R13/Quantity | 3000         |

#### NOTE:

- 1. R7 = 7 INCH LOCK REEL, R13 = 13 INCH LOCK REEL.

- 2. ALL DIMENSIONS ARE DISPLAYED IN MILLIMETERS.