## TMDS Regenerator

The ISL54105 is a high-performance TMDS timing regenerator containing a programmable equalizer and a clock data recovery (CDR) function for each of the 3 TMDS pairs in an HDMI or DVI signal. The TMDS data outputs of the ISL54105 are regenerated and perfectly aligned to the regenerated TMDS clock signal, creating an extremely clean, low-jitter DVI/HDMI signal that can be easily decoded by any TMDS receiver.

The ISL54105 can be used as a cable extender, to clean up a noisy/jittery TMDS source, or to provide a very stable TMDS signal to a finicky DVI or HDMI receiver.

#### Features

- · Clock Data Recovery and Retiming

- · Programmable pre-emphasis on output driver

- Programmable internal  $50\Omega$ ,  $100\Omega$ , or high-Z termination

- Stand-alone or I<sup>2</sup>C software-controlled operation

- 72 lead, 10mm x 10mm QFN package

- Pb-free (RoHS compliant)

## **Applications**

- · DVI/HDMI extenders

- · Televisions/PC monitors/projectors

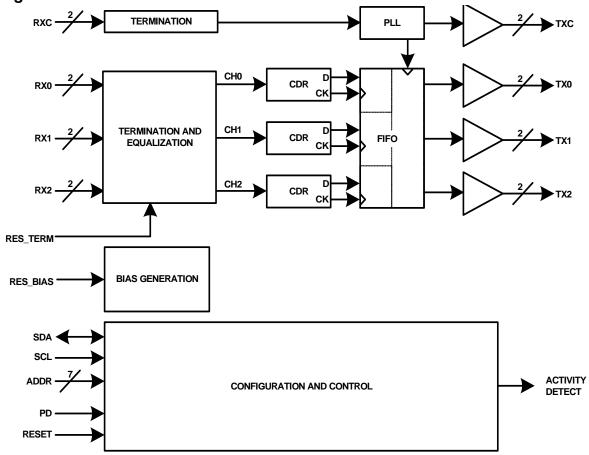

## **Block Diagram**

## **Ordering Information**

| PART NUMBER | TEMP. RANGE (°C) | PACKAGE             | PKG. DWG. # |

|-------------|------------------|---------------------|-------------|

| ISL54105CRZ | 0 to +70         | 72 Ld QFN (Pb-Free) | L72.10x10B  |

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### **Absolute Maximum Ratings**

| )\ |

|----|

| ß۷ |

|    |

| )\ |

| ıΑ |

|    |

| SS |

| SS |

|    |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| QFN Package                                      | 27                     |

| Maximum Biased Junction Temperature              | +125°C                 |

| Storage Temperature                              | 65°C to +150°C         |

| Pb-Free Reflow Profile                           | .see link below        |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

### **Recommended Operating Conditions**

| Temperature    | . 0°C to +70°C |

|----------------|----------------|

| Supply Voltage | $V_{D} = 3.3V$ |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

$\label{eq:continuous} \textbf{Electrical Specifications} \quad \text{Specifications apply for $V_D = 3.3$V$, pixel rate = $165$MHz$, $T_A = +25°C$, $RES_TERM = $1$k$\Omega$, $RES_BIAS = $3.16$k$\Omega$, $TMDS$ output load = $50$\Omega$, $TMDS$ output termination voltage $V_{TERM} = 3.3$V$ unless otherwise noted.$

| SYMBOL                | PARAMETER                                | COMMENT                                         | MIN<br>(Note 2)         | TYP | MAX<br>(Note 2)         | UNIT       |

|-----------------------|------------------------------------------|-------------------------------------------------|-------------------------|-----|-------------------------|------------|

| FULL CHAN             | NEL CHARACTERISTICS                      |                                                 | •                       |     |                         |            |

| f <sub>DATA_MAX</sub> | Maximum Rx Clock Frequency/Pixel Rate    | (Note 3)                                        | 165                     | 225 |                         | MHz        |

| f <sub>DATA_MIN</sub> | Minimum Rx Clock Frequency/Pixel Rate    |                                                 |                         |     | 25                      | MHz        |

| TMDS RECE             | IVER CHARACTERISTICS                     |                                                 | 1                       |     | 1                       |            |

| V <sub>SENS</sub>     | Minimum Differential Input Sensitivity   |                                                 |                         | 50  | 150                     | $mV_{P-P}$ |

| R <sub>50</sub>       | 50Ω Termination Resistance               |                                                 | 45                      | 50  | 55                      | Ω          |

| R <sub>100</sub>      | 100Ω Termination Resistance              |                                                 | 90                      | 97  | 110                     | Ω          |

| CLK <sub>DUTY</sub>   | Rx Clock Duty Cycle                      |                                                 | 20                      |     | 80                      | %          |

| TMDS TRAN             | SMITTER CHARACTERISTICS                  |                                                 |                         |     |                         |            |

| JTX_CLOCK             | Total Jitter on Clock Outputs            | Independent of incoming jitter                  |                         | 32  |                         | ps         |

| JTX_DATA              | Total Jitter on Data Outputs             | Independent of incoming jitter                  |                         | 52  |                         | ps         |

| SKEW <sub>INTRA</sub> | Intra-Pair (+ to -) Differential Skew    |                                                 |                         | ±4  |                         | ps         |

| SKEW <sub>INTER</sub> | Inter-Pair (channel-to-channel) Skew     | Added with respect to incoming inter-pair skew  |                         |     | 2                       | UI         |

| t <sub>RISE</sub>     | Rise Time into $50\Omega$ Load to $3.3V$ | 20% to 80%                                      | 80                      |     | 240                     | ps         |

| t <sub>FALL</sub>     | Fall Time into 50Ω Load to 3.3V          | 20% to 80%                                      | 80                      |     | 240                     | ps         |

| TX V <sub>OH</sub>    | Single-Ended High Level Output Voltage   |                                                 | V <sub>TERM</sub> - 10  |     | V <sub>TERM</sub> + 10  | mV         |

| TX V <sub>OL</sub>    | Single-Ended Low Level Output Voltage    |                                                 | V <sub>TERM</sub> - 600 |     | V <sub>TERM</sub> - 400 | mV         |

| DIGITAL SCI           | HMITT INPUT CHARACTERISTICS              | l                                               |                         |     | 1                       |            |

| V <sub>IH</sub>       | High Threshold Voltage                   |                                                 | 2.0                     |     |                         | V          |

| $V_{IL}$              | High to Low Threshold Voltage            |                                                 |                         |     | 0.8                     | V          |

| I                     | Input Leakage Current                    |                                                 |                         | ±10 |                         | nA         |

| R <sub>PU</sub>       | Internal Pull-Up Resistance              | SDA and SCL pins                                |                         | 65  |                         | kΩ         |

| R <sub>PD</sub>       | Internal Pull-Down Resistance            | AUTO_CH_SEL, CH_SEL_x,<br>RESET, ADDRx, PD pins |                         | 60  |                         | kΩ         |

| C <sub>IN</sub>       | Input Capacitance                        |                                                 |                         | 5   |                         | pF         |

## **Electrical Specifications**

Specifications apply for V<sub>D</sub> = 3.3V, pixel rate = 165MHz, T<sub>A</sub> = +25°C, RES\_TERM = 1k $\Omega$ , RES\_BIAS = 3.16k $\Omega$ , TMDS output load = 50 $\Omega$ , TMDS output termination voltage V<sub>TERM</sub> = 3.3V unless otherwise noted.

| SYMBOL              | PARAMETER                                                     | COMMENT                                                                    | MIN<br>(Note 2) | TYP  | MAX<br>(Note 2) | UNIT |

|---------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|------|-----------------|------|

| DIGITAL OU          | TPUT CHARACTERISTICS                                          |                                                                            |                 |      |                 |      |

| V <sub>OH</sub>     | Output HIGH Voltage, I <sub>O</sub> = 8mA                     |                                                                            | 2.4             |      |                 | V    |

| V <sub>OL</sub>     | Output LOW Voltage, I <sub>O</sub> = -8mA                     |                                                                            |                 |      | 0.4             | V    |

| POWER SUI           | PPLY REQUIREMENTS                                             |                                                                            |                 |      | 1               | 1    |

| V <sub>D</sub>      | Supply Voltage                                                |                                                                            | 3               | 3.3  | 3.6             | V    |

| I <sub>D</sub>      | Supply Current                                                | Inputs driven by 165Mpixel/s<br>TMDS signals.<br>Default register settings |                 | 357  | 405             | mA   |

| I <sub>D</sub>      | Supply Current in Power-down Mode                             | All available inputs driven by 165Mpixel/s TMDS signals.                   |                 | 20   | 26              | mA   |

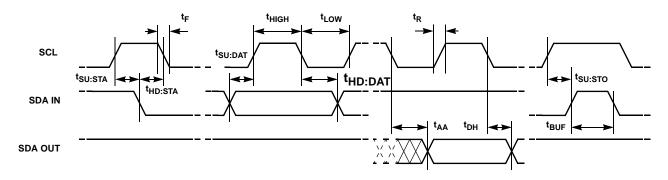

| AC TIMING           | CHARACTERISTICS (2-WIRE INTERFACE)                            |                                                                            |                 |      |                 |      |

| f <sub>SCL</sub>    | SCL Clock Frequency                                           |                                                                            | 0               |      | 400             | kHz  |

| t <sub>AA</sub>     | SCL LOW to SDA Data Out Valid                                 |                                                                            |                 | 200  | 470             | ns   |

| t <sub>BUF</sub>    | Time the Bus Must be Free Before a New Transmission Can Start |                                                                            | 1.3             |      |                 | μs   |

| t <sub>LOW</sub>    | Clock LOW Time                                                |                                                                            | 1.3             | 0.1  |                 | μs   |

| tHIGH               | Clock HIGH Time                                               |                                                                            | 0.6             | 0.2  |                 | μs   |

| t <sub>SU:STA</sub> | Start Condition Setup Time                                    |                                                                            | 0.6             | 0.03 |                 | μs   |

| t <sub>HD:STA</sub> | Start Condition Hold Time                                     |                                                                            | 0.6             | 0.07 |                 | μs   |

| t <sub>SU:DAT</sub> | Data In Setup Time                                            |                                                                            | 100             | 0.03 |                 | ns   |

| t <sub>HD:DAT</sub> | Data In Hold Time                                             |                                                                            | 0               |      |                 | ns   |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                                     |                                                                            | 0.6             |      |                 | μs   |

| t <sub>DH</sub>     | Data Output Hold Time                                         |                                                                            | 160             |      |                 | ns   |

#### NOTE:

- 2. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 3. Operation up to 165MHz is guaranteed. While many parts will typically operate up to 225MHz, operation above 165MHz is not guaranteed.

FIGURE 1. 2-WIRE INTERFACE TIMING

3

FN6723.0 June 11, 2008

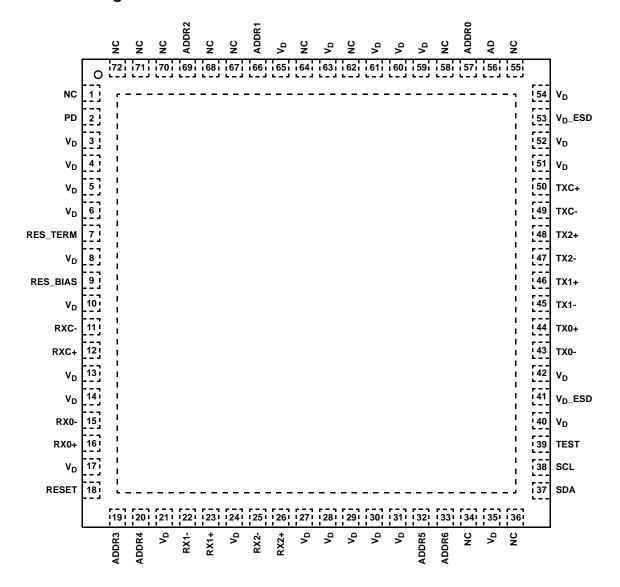

## **ISL54105 Pin Configuration**

## Pin Descriptions

| SYMBOL                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RX0-, RX0+, RX1-, RX1+, RX2-, RX2+ | TMDS Inputs. Incoming TMDS data signals.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RXC-, RXC+                         | TMDS Inputs. Incoming TMDS clock signals.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TX0-, TX0+, TX1-, TX1+, TX1-, TX1+ | TMDS Outputs. TMDS output data for selected channel.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TXC-, TXC+                         | TMDS Outputs. TMDS output clock for selected channel.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SCL                                | Digital input, 5V tolerant, 500mV hysteresis. Serial data clock for 2-wire interface. Note: Internal $65k\Omega$ pull-up to $V_D$ .                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SDA                                | Bidirectional Digital I/O, open drain, 5V tolerant. Serial data I/O for 2-wire interface. Note: Internal $65k\Omega$ pull-up to $V_D$ .                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ADDR[6:0]                          | Digital inputs, 5V tolerant. 7-Bit address for serial interface.  Note: Internal 60kΩ pull-down to GND.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| AD                                 | Digital Output, 3.3V. AD = Activity Detect. Output goes high when an active TMDS clock is detected on RXC.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| RES_BIAS                           | Tie to GND through a 3.16k external resistor. Sets up internal bias currents.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| RES_TERM                           | Tie to VD through a 1.0k 1% external resistor. During calibration, the termination resistor closest in value to RES_TERM/20 (= $50\Omega$ ) is selected.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PD                                 | Digital Input, 3.3V. PD = Power-down. Pull high to put the ISL54105 in a minimum power consumption mode.<br><b>Note:</b> To ensure proper operation, this pin must be held low during power-up. It may be taken high 100ms after the power supplies have settled to 3.3V $\pm$ 10%. When exiting Power-down, a termination resistor Recalibration cycle must be run to re-trim the termination resistors (see register 0x03[7]). Note: Internal $60k\Omega$ pull-down to GND. |  |  |  |

| RESET                              | Digital Input, 3.3V. Pull high then low to reset the mux. Tie to GND in final application. Note: Internal 60kΩ pull-down to GND.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| TEST                               | Digital Input. Used for production testing only. Tie to GND in final application. This pin has an internal pulldown to GND, so it is also acceptable to leave this pin floating.                                                                                                                                                                                                                                                                                              |  |  |  |

| V <sub>D</sub>                     | Power supply. Connect to a 3.3V supply and bypass each pin to GND with 0.1µF.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| V <sub>D</sub> _ESD                | Power supply for ESD protection diodes. Connect one of these pins (pin 41 or 53) to the 3.3V $V_D$ supply rail with a low $V_F$ (0.4V or lower) Schottky diode, with the cathode connected to $V_D$ _ESD and the anode connected to $V_D$ . Bypass each pin to GND with 0.1 $\mu$ F.                                                                                                                                                                                          |  |  |  |

| THERMAL PAD (GND)                  | Ground return for the entire chip. The thermal pad must have a low impedance connection to GND for the ISL54105 to function at all. The lower electrical impedance, the better the ground, and the better the performance. A low thermal impedance between the thermal pad and the GND plane of the PCB will dissipate the heat from the package more efficiently as well and is recommended.                                                                                 |  |  |  |

FN6723.0 June 11, 2008

# Register Listing

| ADDRESS | REGISTER (DEFAULT VALUE)                       | BIT(S) | FUNCTION NAME                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------|--------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00    | Device ID (read only)                          | 3:0    | Device Revision                  | 1 = initial silicon, 2 = second revision, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                                | 7:4    | Device ID                        | 3 = ISL54105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x01    | Channel Activity Detect (read only)            | 1:0    | Reserved                         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                                                | 2      | Activity Detect                  | 0: TMDS clock not present on RXC<br>1: TMDS clock detected on RXC                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x02    | Channel Selection (0x0C)                       | 3:0    | Reserved                         | This nibble should always be set to 0xC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                                                | 4      | Reset                            | Full chip reset. Write a 1 to reset. Will set itself to 0 when reset is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |                                                | 5      | Power-down                       | 0: Normal Operation 1: Puts the chip in a minimal power consumption mode, turning off all TMDS outputs and open-circuiting all TMDS inputs.  This bit is OR'ed with the Power-down input pin. If either is set, the chip will enter power-down. Serial I/O stays operational in PD mode.  Note: When exiting Power-down, a termination resistor Recalibration cycle must be run to re-trim the termination resistors (see register 0x03[7]).                                                                                         |

| 0x03    | Input Control (0x12) Recommended default: 0x63 | 0      | Reserved                         | Set to 1. Default value of 0 is OK, set to 1 to slightly reduce power consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |                                                | 1      | Reserved                         | Set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |                                                | 2      | Tri-state Clock<br>Inputs        | 0: Clock inputs are terminated into $50\Omega/100\Omega$ .<br>1: Clock inputs are tri-stated (to allow chip to operate in parallel with another TMDS receiver with fixed $50\Omega$ termination)                                                                                                                                                                                                                                                                                                                                     |

|         |                                                | 3      | Tri-state Data Inputs            | 0: Data inputs are terminated into $50\Omega/100\Omega$ .<br>1: Data inputs are tri-stated (to allow chip to operate in parallel with another TMDS receiver with fixed $50\Omega$ termination)                                                                                                                                                                                                                                                                                                                                       |

|         |                                                | 4      | Activity Detect Mode             | 0: AC Activity. Activity detection is based on the presence of AC activity on TMDS clock inputs. This setting (along with a hysteresis of 20mV enabled) provides reliable activity detection. (recommended setting)  1: Common Mode Voltage. If the common mode voltage is above ~3.05V, the input is considered in active. This method has been found to be unreliable with small signal swings and should not be used. This setting is the silicon default but should be changed in software for more reliable activity detection. |

|         |                                                | 5      | Clock Rx Hysteresis              | Enables hysteresis for the clock inputs to prevent false clock detection when both inputs are high. Data inputs do not get hysteresis.  0: TMDS input hysteresis disabled  1: TMDS input hysteresis enabled. Eliminates false activity detects on unconnected channels. (recommended setting)                                                                                                                                                                                                                                        |

|         |                                                | 6      | Clock Rx Hysteresis<br>Magnitude | Controls the amount of hysteresis in the clock inputs. 0: 10mV 1: 20mV (recommended setting)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |                                                | 7      | Recalibrate                      | 0: Normal Operation 1: Recalibrates termination resistance. To recalibrate, take this bit high, wait at least 1ms, then take this bit low. Calibration is automatically done after power-on, but performing a recalibration after the supply voltage and temperature have stabilized may result in termination resistances closer to the desired $50\Omega$ .                                                                                                                                                                        |

FN6723.0 June 11, 2008 intersil

6

# Register Listing (Continued)

| ADDRESS | REGISTER (DEFAULT VALUE)      | BIT(S) | FUNCTION NAME                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-------------------------------|--------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x04    | Termination Control (0x00)    | 1:0    | Reserved                      | Set to 00.                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |                               | 2      | Data Termination              | 0: TMDS Data inputs terminated into $50\Omega$ (normal operation) 1: TMDS Data inputs terminated into $100\Omega$ (for paralleled inputs)                                                                                                                                                                                                                                                                    |

|         |                               | 5:3    | Reserved                      | Set to 000.                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                               | 6      | Clk Termination               | 0: TMDS Clock inputs terminated into $50\Omega$ (normal operation) 1: TMDS Clock inputs terminated into $100\Omega$ (for paralleled inputs)                                                                                                                                                                                                                                                                  |

|         |                               | 7      | Reserved                      | Set to 0.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x05    | Output Options (0x00)         | 0      | Tri-state Clock<br>Outputs    | Normal Operation     Clock outputs tri-stated (allows another chip to drive the output clock pins)                                                                                                                                                                                                                                                                                                           |

|         |                               | 1      | Tri-state Data<br>Outputs     | O: Normal Operation     Data outputs tri-stated (allows another chip to drive the output data pins)                                                                                                                                                                                                                                                                                                          |

|         |                               | 2      | Invert Output<br>Polarity     | 0: Normal Operation 1: The polarity of the TMDS data outputs is inverted (+ becomes -, - becomes +). TMDS clock unchanged.                                                                                                                                                                                                                                                                                   |

|         |                               | 3      | Reverse Output<br>Order       | 0: Normal Operation 1: CH0 data is output on CH2 and CH2 data is output on CH0. No change to CH1.                                                                                                                                                                                                                                                                                                            |

| 0x06    | Data Output Drive (0x00)      | 3:0    | Transmit Current              | Transmit Drive Current for data signals, adjustable in 0.125mA steps. Clock current is fixed at 10mA. 0x0: 10mA 0x8: 11mA 0xF: 11.875mA                                                                                                                                                                                                                                                                      |

|         |                               | 7:4    | Transmit<br>Pre-emphasis      | Drive boost (in 0.125mA steps) added during first half of each bit period for data signals. Clock signals do not have pre-emphasis.  0x0: 0mA  0x8: 1mA  0xF: 1.875mA                                                                                                                                                                                                                                        |

| 0x07    | Reserved (0xCC)               | 7:0    | Reserved                      | Default value of 0xCC is OK, can also be set to 0x00.                                                                                                                                                                                                                                                                                                                                                        |

| 0x08    | Equalization (0xCC)           | 3:0    | Equalizer Gain                | Boost (dB) = 1dB + <gain value=""> * 0.8dB</gain>                                                                                                                                                                                                                                                                                                                                                            |

|         |                               |        |                               | 0x0: 1dB boost at 800MHz<br>0xC: 10.6dB boost at 800MHz (default)<br>0xF: 13dB boost at 800MHz                                                                                                                                                                                                                                                                                                               |

|         |                               | 7:4    | Reserved                      | Default value of 0xC is OK, can also be set to 0x0.                                                                                                                                                                                                                                                                                                                                                          |

| 0x09    | Test Pattern Generator (0x00) | 1:0    | Generator Mode                | When a 25MHz to 165MHz clock is applied to the clock input, this function will output a PRBS7 pattern on the TX pins.  0: Normal operation (test patterns disabled)  1: PRBS7 pattern  2: Low frequency toggle (0000011111)  3: High frequency toggle (1010101010)  Note: When switching from the high frequency toggle pattern to the low frequency toggle pattern, you must first select normal operation. |

|         |                               | 2      | Enable PRBS7 Error<br>Counter | Enables PRBS7 error counter in registers 0x0A to 0x0C. 0: Disable PRBS7 Error Counter 1: Enable PRBS7 Error Counter                                                                                                                                                                                                                                                                                          |

# Register Listing (Continued)

| ADDRESS | REGISTER (DEFAULT VALUE)                       | BIT(S) | FUNCTION NAME                 | DESCRIPTION                                                                                                                                                                                       |

|---------|------------------------------------------------|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0A    | PRBS7 Error Counter Link 0 (read only)         | 7:0    | PRBS7 Error<br>Counter Link 0 | PRBS7 Error Counter of Link 0. Saturates at 0xFF. Reading this register clears this register at end of read                                                                                       |

| 0x0B    | PRBS7 Error Counter Link 1 (read only)         | 7:0    | PRBS7 Error<br>Counter Link 1 | PRBS7 Error Counter of Link 1. Saturates at 0xFF. Reading this register clears this register at end of read                                                                                       |

| 0x0C    | PRBS7 Error Counter Link 2 (read only)         | 7:0    | PRBS7 Error<br>Counter Link 2 | PRBS7 Error Counter of Link 2. Saturates at 0xFF. Reading this register clears this register at end of read                                                                                       |

| 0x10    | PLL Bandwidth (0x10) Recommended default: 0x12 | 1:0    | PLL Bandwidth                 | Selects between 4 PLL bandwidth settings 0: 4MHz (silicon default) 1: 2MHz 2: 1MHz (recommended default) 3: 500kHz 1MHz provides slightly better performance with high jitter/high noise signals. |

|         |                                                | 7:2    | Reserved                      | Keep set to 000100 binary.                                                                                                                                                                        |

intersil

## Application Information

The ISL54105 is a TMDS regenerator, locking to the incoming DVI or HDMI signal with triple Clock Data Recovery units (CDRs) and a Phase Locked Loop (PLL). The PLL generates a low jitter pixel clock from the incoming TMDS clock. The TMDS data signals are equalized, sliced by the CDR, re-aligned to the PLL clock, and sent out the TMDS outputs.

#### **Activity Detection**

The TMDS input is considered active using one of two methods. The original default activity detect method (register 0x03b4 = 1) is to measure the common mode of the TMDS clock input for each channel. If the common mode is 3.3V, it indicates that there is nothing connected to that input, or that whatever is connected is turned off (inactive). This has been found to be relatively unreliable, particularly with weak signals.

The preferred method of activity detection is looking for an active AC signal on the TMDS clock input for that channel (register 0x03b4 = 1). This is more robust, however disconnected inputs will cause both inputs to the differential receiver to be the same level - 3.3V. If the offset error of the differential TMDS receiver is very small, the receiver can not resolve a 1 or a 0 and will randomly switch between states, which may be detected as an active clock. Register 0x03 bits 5 and 6 allow a 10mV or 20mV offset to be added to the input stage of the clock inputs, eliminating this problem. This offset will slightly reduce the sensitivity of TMDS receiver for the clock lines, but since the clock signals are much lower frequency than the data, they will not be nearly as attenuated, so this is not a problem in practice.

Again, using the AC activity detection method (register 0x03b4 = 0) is recommended.

### Rx Equalization

Register 0x08 bits 3:0 control the amount of equalization applied to the TMDS inputs, providing 4 bits of control. The equalization range available is from a minimum of 1dB boost to a maximum of 13dB at 800MHz, in 0.8dB increments. Ideally, the equalization is adjusted in the final application to provide optimal performance with the specific DVI/HDMI transmitter and cable used. In general, the amount of equalization required is proportional to the cable length. If the equalization must be fixed (can not be adjusted in the final application), an equalization setting of 0xA works well with short cables as well as medium to longer cables.

#### Tx Pre-emphasis

The transmit pre-emphasis function sinks additional current during the first bit after every transition, increasing the slew rate for a given capacitance, and helping to maintain the slew rate when using longer/higher capacitance cables. Pre-emphasis is controlled by register 0x06 bits 7:4, and ranges from a minimum of 0mA (no pre-emphasis) to 1.875mA (max pre-emphasis).

### PLL Bandwidth

The 2-bit PLL Bandwidth register controls the loop bandwidth of the PLL used to recover the incoming clock signal. The default 4MHz setting works well in most applications, however a lower bandwidth of 1MHz has proven to work just as well with good TMDS sources and slightly better with marginal sources.

#### Power-down

The chip can be placed in a Power-down mode when not in use to conserve power. Setting the Power-down bit (register 0x02 bit 5) to a 1 or pulling the PD input pin high places the chip in a minimal power consumption mode, turning off all TMDS outputs and disconnecting all TMDS inputs. Serial I/O stays operational in PD mode. Note that the PD pin must be low during power-on in order to initialize the I<sup>2</sup>C interface.

Note: When exiting Power-down, a termination resistor Recalibration cycle must be run to re-trim the termination resistors (see register 0x03[7]).

## Typical Performance

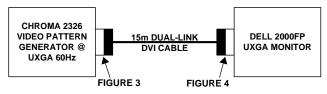

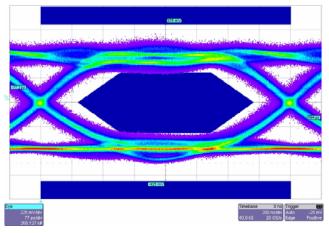

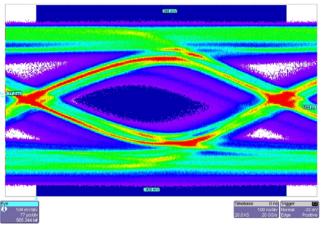

Setup A (Figure 2) was used to capture the TMDS eye diagrams shown in Figure 3 and Figure 4:

FIGURE 2. TEST SETUP A

The 162.5Mpixel/s (UXGA 60Hz) DVI output of the Chroma 2326 was terminated into a TPA2 Plug adapter and measured with a LeCroy differential probe and 6MHz SDA using the LeCroy's software clock recovery. As Figure 3 shows, the amplitude of the TMDS signal is slightly low, but the eye is otherwise acceptable.

FIGURE 3. EYE DIAGRAM AT OUTPUT OF CHROMA GENERATOR

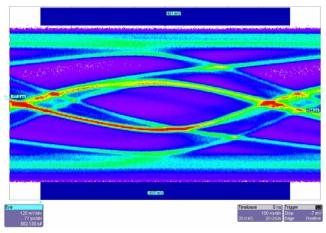

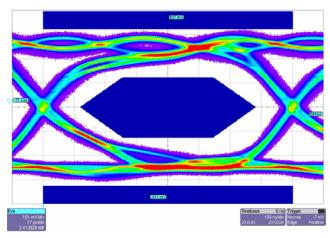

Next, a 15m DualLink DVI cable was attached and terminated into a female TPA2 adapter and the eye captured in Figure 4.

FIGURE 4. CHROMA EYE DIAGRAM AFTER 15m CABLE

The eye is not meeting the minimum requirements of either the HDMI or DVI standards and the Dell Monitor is unable to recover the data and display an image.

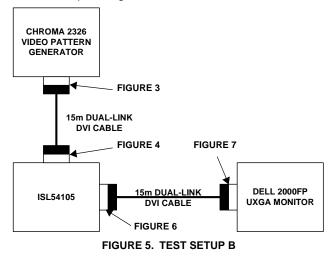

Setup B inserts an ISL54105 and an additional 15m cable between the pattern generator and the monitor:

Given the input signal shown in Figure 4, the ISL54105's TMDS output signal (Figure 6) is extremely clean. The output is an improvement over the original signal coming from the pattern generator in both amplitude and jitter.

FIGURE 6. EYE DIAGRAM AT OUTPUT OF ISL54105

The cleaner signal generated at the output of the ISL54105 results in an improved eye at the end of another 15m cable (Figure 7). The eye is open enough that the Dell 2000FP can now display a UXGA image with no visible sparkle or other artifacts.

FIGURE 7. ISL54105 EYE DIAGRAM AFTER 15m CABLE

## Tx Loading Considerations

When the ISL54105 is powered-up and its Tx outputs are disabled, via either the PD (power-down) pin, the power-down register bit (register 0x02[5]), or the tri-state outputs bits (register 0x05[1:0]), the Tx pins are high impedance. In this state, they will draw no current from the Rx pins of any TMDS receiver they may be connected to.

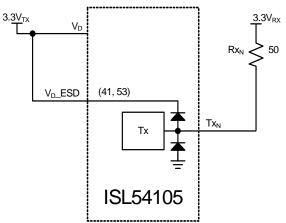

However, if power to the ISL54105 is removed, the Tx pins are no longer high-impedance. Figure 8 shows the relevant equivalent circuit, including the internal ESD protection diodes. For simplicity, only one of the eight Tx outputs, ESD protection diodes, and Rx termination resistors are shown.

When  $V_D$  to the ISL54105 drops below ~2.7V and power is applied to the external TMDS receiver, ESD protection diodes inside the ISL54105 can become forward-biased,

drawing current from the external TMDS receiver it is attached to.

FIGURE 8. ISL54105 ESD PROTECTION DIODES

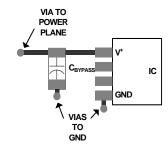

This is non-ideal and can cause the ISL54105 to fail HDMI Compliance Test 7-3 (" $V_{OFF}$ ").  $V_{OFF}$  is the voltage across each  $50\Omega$  Rx<sub>N</sub> resistor when the power is removed from the device containing the ISL54105.

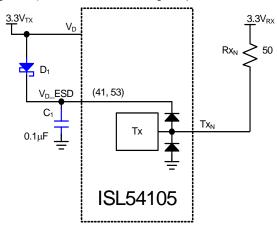

Modifying the PCB layout per Figure 9 to add a Schottky diode between the  $\rm V_D$  power net and the  $\rm V_D$ ESD pins, eliminates current flow from the ESD bus into  $\rm V_D$ . This reduces the amount of current drawn from the Tx supply, but there is still some circuitry attached to the internal ESD bus that will sink some current. So the current drawn from Rx will be lower than if the diode were not there (reducing the  $\rm V_{OFF}$  magnitude), but still not low enough to pass Test 7-3.

FIGURE 9. SCHOTTKY DIODE MODIFICATION

Intersil is currently sampling the ISL54105A, which is fully compliant with Test 7-3 when applied using the circuit shown in Figure 9. The ISL54105A is 100% drop-in and backwards compatible with the ISL54105.

Using the ISL54105A in a layout designed for the ISL54105 (Figure 8) will result in the same behavior as the original version. See Table 1 for the full matrix.

TABLE 1. VERSION/LAYOUT MATRIX

| VERSION   | FIGURE 8  | FIGURE 9                 |

|-----------|-----------|--------------------------|

| ISL54105  | Fails 7-3 | Fails 7-3 (not as badly) |

| ISL54105A | Fails 7-3 | Passes 7-3               |

Intersil recommends adding the Schottky circuit to all designs to reduce Rx current drain in systems using the original version and completely eliminate it in systems using the ISL54105A.

## Inter-Pair (Channel-to-Channel) Skew

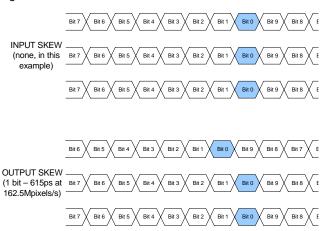

The read pointers for Channel 0, 1, and 2 of the FIFO that follows the CDR all have the same clock, so all 3 channels transition within a few picoseconds of each other - there is essentially no skew between the transitions of the three channels.

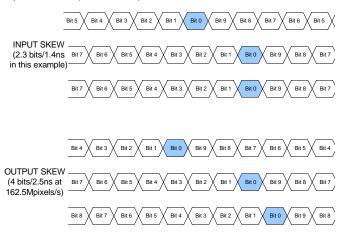

However the FIFO read pointers may be positioned up to 2 bits apart relative to each other, introducing a random, fixed channel-to-channel skew of skew of 1 or (much less frequently) 2 bits. The random skew is introduced whenever there is a discontinuity in the input signal (typically a video mode change or a new mux channel selection). After the CDRs and PLL lock, the skew is fixed until the next discontinuity. This adds up to 2 bits of skew in addition to any incoming skew, as shown in the following examples.

Figure 10 shows an input (the top three signals) with essentially no skew. After the ISL54105 locks on to the signal, there may be 1 bit of skew on the output, as shown in Figure 10.

FIGURE 10. MAXIMUM ADDITIONAL INTERCHANNEL SKEW FOR INPUTS WITH NO OR LITTLE SKEW

When there is pre-existing skew on the input, the ISL54105 can add up to 2 bits to the channel-to-channel skew. In the example in Figure 11, the incoming red channel has 2.3 bits

of skew relative to the incoming green and blue. The FIFO's quantization (worst case) increases the total skew to 4.0 bits.

FIGURE 11. MAXIMUM ADDITIONAL INTERCHANNEL SKEW

FOR INPUTS WITH MODERATE TO LARGE

SKEW

While increasing skew is not desirable, DVI and HDMI receivers are required to have a minimum of 6 bits of inter-pair skew tolerance, so the addition of 2 bits of skew is only a problem with the most pathological cables and transmitters. It does, however, limit the number of ISL54105s that can be put in series (although statistically, it is unlikely that all the skews would line up in a worst-case configuration).

## **PCB Layout Recommendations**

Because of the high speed of the TMDS signals, careful PCB layout is critical to maximize performance. The following guidelines should be adhered to as closely as possible:

- All TMDS pair traces should have a characteristic impedance of  $50\Omega$  with respect to the power/ground planes and  $100\Omega$  with respect to each other. Failure to meet this requirement will increase reflections, shrinking the available eye.

- Avoid vias for all 3 high speed TMDS pairs. Vias add inductance which causes a discontinuity in the characteristic impedance of the trace. Keep all the traces on the top (or the bottom) of the PCB. The TMDS clock can have vias if necessary, since it is lower speed and less critical. If you must use a via, ensure the vias are symmetrical (put identical vias in both lines of the differential pair).

- For each TMDS channel, the trace lengths of the 3 TMDS pairs (0, 1 and 2) should ideally be the same to reduce inter channel skew introduced by the board.

- The trace length of the clock pair is not critical at all.

Since the clock is only used as a frequency reference, its phase/delay is inconsequential. In addition, since the TMDS clock frequency is 1/10th the pixel rate, the clock signal itself is much more noise-immune. So liberties

- (such as vias and circuitous paths) can be taken when routing the clock lines.

- Minimize capacitance on all TMDS lines. The lower the capacitance, the sharper the rise and fall times.

- Maintain a constant, solid ground (or power) plane under the 3 high speed TMDS signals. Do not route the signals over gaps in the ground plane or over other traces.

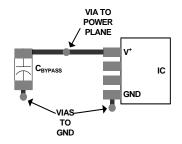

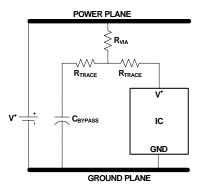

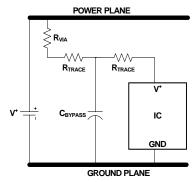

- Ideally each supply should be bypassed to ground with a 0.1µF capacitor. Minimize trace length and vias to minimize inductance and maximize noise rejection. Figure 12 demonstrates a common but non-ideal PCB layout and its equivalent circuit. The additional trace resistance between the bypass capacitor and the power supply/IC reduces its effectiveness. Figure 13 demonstrates a better layout. In this case there is still series trace resistance (it is impossible to completely eliminate it), but now it is being put to good use, as part of a "T" filter, attenuating supply noise before it gets to the IC, and reducing the amount of IC-generated noise that gets injected into the supply. Follow the good supply bypassing rules shown in Figure 13 to the extent possible.

**EQUIVALENT CIRCUIT**

FIGURE 12. SUB-OPTIMAL BYPASS CAPACITOR LAYOUT

**EQUIVALENT CIRCUIT**

FIGURE 13. OPTIMAL ("T") BYPASS CAPACITOR LAYOUT

#### ISL54105 Serial Communication

#### Overview

The ISL54105 uses a 2-wire serial bus for communication with its host. SCL is the Serial Clock line, driven by the host and SDA is the Serial Data line, which can be driven by all devices on the bus. SDA is open drain to allow multiple devices to share the same bus simultaneously.

Communication is accomplished in three steps:

- 1. The Host selects the ISL54105 it wishes to communicate with.

- The Host writes the initial ISL54105 Configuration Register address it wishes to write to or read from.

- 3. The Host writes to or reads from the ISL54105's Configuration Register. The ISL54105's internal address pointer auto increments, so to read registers 0x00 through 0x1B, for example, one would write 0x00 in step 2, then repeat step three 28 times, with each read returning the next register value.

The ISL54105 has a 7-bit address on the serial bus, determined by the ADDR0-ADDR6 bits. This allows up to 128 ISL54105s to be independently controlled by the same serial bus.

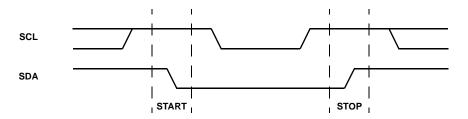

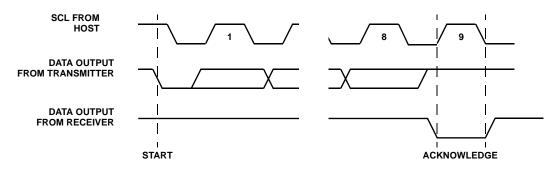

The bus is nominally inactive, with SDA and SCL high. Communication begins when the host issues a START command by taking SDA low while SCL is high (Figure 14). The ISL54105 continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met. The host then transmits the 7-bit serial address plus a  $R/\overline{W}$  bit, indicating if the next transaction will be a Read ( $R/\overline{W}=1$ ) or a Write ( $R/\overline{W}=0$ ). If the address transmitted matches that of any device on the bus, that device must respond with an ACKNOWLEDGE (Figure 15).

Once the serial address has been transmitted and acknowledged, one or more bytes of information can be written to or read from the slave. Communication with the selected device in the selected direction (read or write) is ended by a STOP command, where SDA rises while SCL is high (Figure 14), or a second START command, which is commonly used to reverse data direction without relinquishing the bus.

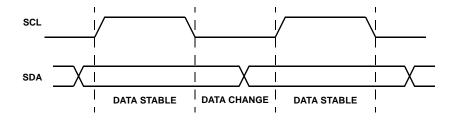

Data on the serial bus must be valid for the entire time SCL is high (Figure 16). To achieve this, data being written to the ISL54105 is latched on a delayed version of the rising edge of SCL. SCL is delayed and deglitched inside the ISL54105 for three crystal clock periods (120ns for a 25MHz crystal) to eliminate spurious clock pulses that could disrupt serial communication.

When the contents of the ISL54105 are being read, the SDA line is updated after the falling edge of SCL, delayed and deglitched in the same manner.

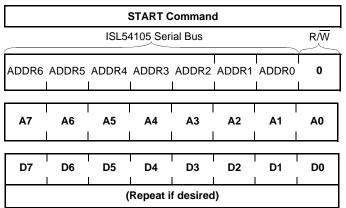

#### Configuration Register Write

Figure 17 shows two views of the steps necessary to write one or more words to the Configuration Register.

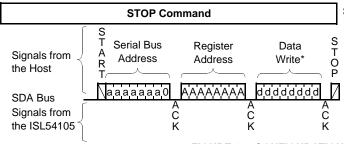

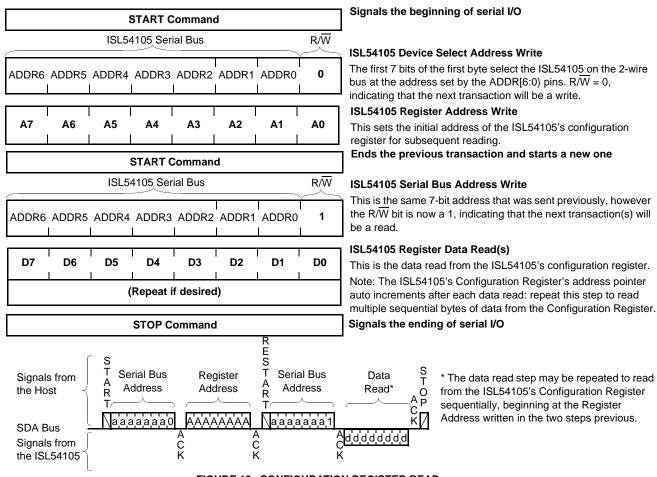

#### Configuration Register Read

Figure 18 shows two views of the steps necessary to read one or more words from the Configuration Register.

FIGURE 14. VALID START AND STOP CONDITIONS

FIGURE 15. ACKNOWLEDGE RESPONSE FROM RECEIVER

FIGURE 16. VALID DATA CHANGES ON THE SDA BUS

#### Signals the beginning of serial I/O

#### ISL54105 Device Select Address Write

The first 7 bits of the first byte select the ISL54105 on the 2-wire bus at the address set by the ADDR[6:0} pins. The R/W bit is a 0, indicating that the next transaction will be a write.

#### ISL54105 Register Address Write

This is the address of the ISL54105's configuration register that the following byte will be written to.

#### ISL54105 Register Data Write(s)

This is the data to be written to the ISL54105's configuration register. Note: The ISL54105's Configuration Register's address pointer auto increments after each data write: repeat this step to write multiple sequential bytes of data to the Configuration Register.

14

#### Signals the ending of serial I/O

\* The data write step may be repeated to write to the ISL54105's Configuration Register sequentially, beginning at the Register Address written in the previous step.

FIGURE 17. CONFIGURATION REGISTER WRITE

FIGURE 18. CONFIGURATION REGISTER READ

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

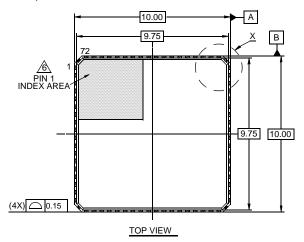

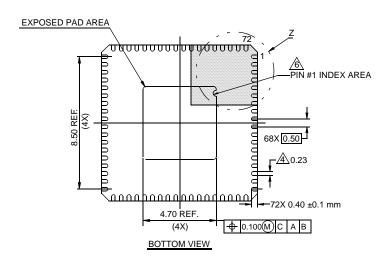

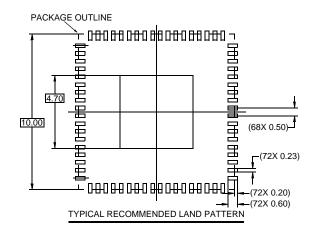

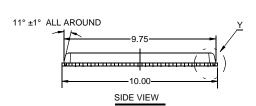

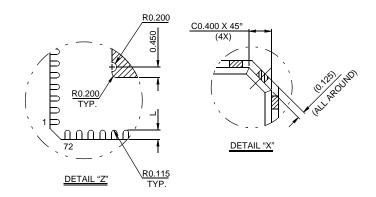

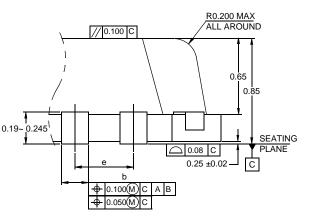

## **Package Outline Drawing**

#### L72.10x10B

72 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE (PUNCH QFN) Rev 0, 5/07

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to JESD-MO220.

- Unless otherwise specified, tolerance: Decimal ± 0.05; body tolerance: ±0.1mm

- Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

DETAIL "Y"